在微机系统中,微处理器的强大功能必须通过外部设备才能实现,而外设与微处理器之间的信息交换及通信又是靠接口实现的,所以,微机应用系统的研究和微机系统的产品的开发,从硬件角度来讲,就是接口技术的演进和开发。微机的应用随着外设的不断更新早已深入各个领域。

第一章 概述

预备知识

CPU架构分类

目前市面上的CPU分类主要分有两大阵营,一个是intel、AMD为首的复杂指令集CPU,另一个是以IBM、ARM为首的精简指令集CPU。

Intel、AMD的CPU是X86、x64架构的,而IBM公司的CPU是PowerPC架构,ARM公司是ARM架构

而对于Intelx86架构的CPU,最具代表性的就是1978年所推出的Intel 8086和之后推出的Intel 8088,被称为x86架构的鼻祖。

8086:16位处理器芯片,内部总线和外部总线都为16位,本笔记中的接口都是基于8086架构的。

8088:准16位处理器芯片,内部总线16位,外部总线8位总线位数

内部总线:CPU位数,CPU一次处理的数据总线宽度,通用寄存器长度,ALU运算字长。

外部总线:系统总线位数,与内存交换数据的宽度,即数据总线。

注:内、外都是相对CPU而言的。

三总线:数据总线、地址总线、控制总线。

8086中,数据总线16位,地址总线20位,寻址空间2^{20}=1MB。主板芯片组

CPU与周边设备沟通的桥梁,分为南桥和北桥。

南桥:PCI桥,CPU与外设的I/O。

北桥:HOST桥,离CPU更近,速率更快,用于CPU和内存、显卡、PCI桥交换数据。

接口概念

接口指CPU与外设间信息交换的输入输出电路,CPU<->接口<->外设。

接口实现了外设与微机间的信息交换。

三类接口芯片

通用接口芯片:并行接口、串行接口等。

面向微机专用接口芯片:不直接与外设连接,只是帮CPU分担工作,DMA控制器、中断控制器等。

面向外设专用接口芯片:显示器接口、键盘接口等。设立接口原因

CPU与外设两者的工作速度不兼容

CPU与外设两者的信号不兼容

有利于外设的标准化接口电路一般结构

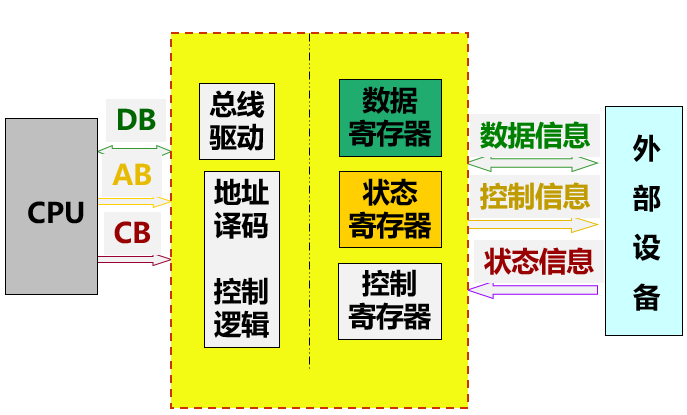

DB, AB, CB即数据总线、地址总线、控制总线。

接口内主要有三类寄存器:命令口(CPU向其中写命令,只写)、状态口(CPU从其中读取接口的状态信息,只读)、数据口(CPU与外设间的交换信息,可读可写)。CPU与接口交换数据方式

程序控制方式:CPU主动。无条件传送方式(同步传送),外设一直是准备好的,传送前CPU不需要了解外设的状态,适合一些较简单的外设,如LED显示器;查询传送方式(条件传送),传数据前CPU先检测外设状态(状态字),外设没准备好,CPU就一直等待。

中断方式:外设主动,CPU被动。外设做好准备时,主动向CPU发出中断请求,CPU响应中断。

DMA方式:DMA控制外设与存储器间的数据传送,传送过程由特定硬件完成,无需CPU介入。

第二章 I/O端口地址译码技术

端口地址

I/O端口(Port):指I/O接口电路中能被CPU直接访问的寄存器,CPU与外设间不能直接交换信息,必须通过端口。

端口编址方式

采用小端模式,低字节在低地址,高字节在高地址。

统一编址:端口地址和存储器地址是统一的,可直接用内存指令访问端口,无需专门的I/O指令。因此指令会比较长,且寻址速度慢。

独立编址:端口地址和存储器地址独立,根据不同指令访问不同的地址(通过专门的I/O指令访问端口),8086中就是这种方式。8086中端口地址分配

地址空间:000-3FFH,A0-A9共10根地址线,可访问1024个端口。3FFH=15+15*16+3*16*16=1023。

系统板上的I/O接口芯片:地址000-0FFH,单字节地址。较为简单的接口,定时器、中断控制器等。

扩展槽上的I/O接口卡:地址100-3FFH,双字节地址。若干个集成电路合在一起,较为复杂,显卡、声卡、网卡等。端口地址译码方式

三种译码方式:全译码、部分译码和地址开关译码。

全译码:所有I/O地址线A0~A9全部作为译码的输入参与译码。

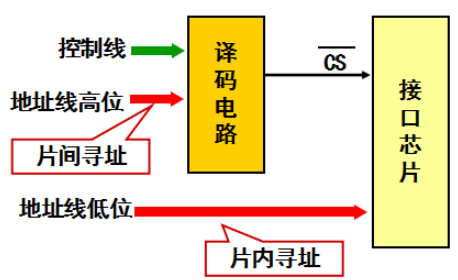

部分译码:将地址线分为两部分:端口地址=芯片地址(高位)+片内地址(低位),只有高位地址线参加译码,可分为片间寻址与片内端口寻址。片间寻址:高位地址信号与控制信号组合,经译码电路产生接口的片选信号\(\small \overline{CS}\)。控制信号如:读信号\(\small \overline{IOR}\)、写信号\(\small \overline{IOW}\)等。片内端口寻址:低位地址信号不参加译码,直接连到接口芯片中,进行端口寻址。

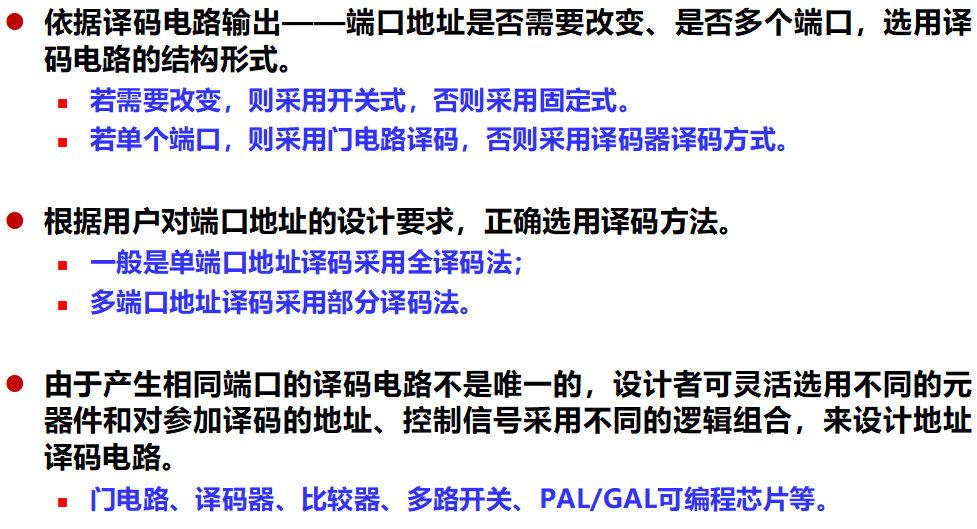

地址开关译码:在部分译码方法的基础上,加上地址开关来改变端口地址。地址译码电路设计

固定式译码:接口中用到的端口地址不能更改,分为门电路译码和译码器译码。门电路译码:对单一端口地址进行译码,使用与门、与非门等各种门电路;译码器译码:对多个端口地址译码,使用各种译码器元件。

可选式译码:采用开关式端口地址译码。通过开关改变接口卡的端口地址(无需改动线路)。如果要求端口地址能适应不同的地址分配场合,或为系统以后扩充留有余地,则采用开关式端口地址译码,电路可由地址开关、译码器、比较器或异或门几种元器件组合而成。

地址译码电路设计原则如下:

接口I/O指令

8086中通过AL寄存器与外设交换信息。

- 端口为单字节地址:可直接使用地址。

in AL, 60H:将60H端口中的8位数据->AL;out 61H, AL:将AL中数据->61H端口。 - 端口为双字节地址:不能直接使用地址,通过DX寄存器承接。

mov DX,300H in AL,DX:将300H端口中的8位数据->AL(地址为16位,数据还是8位)。mov DX,301H out DX,AL:将AL中数据->301H端口。

注:in/out都是相对CPU而言的。

第三章 定时/计数技术

- 什么是定时与计数

定时:确定时间间隔。

计数:统计个数。

在计算中定时就是对时钟脉冲(CLK)进行计数,定时和计数本质是一样的。

定时计数接口82C54

可编程定时计数器

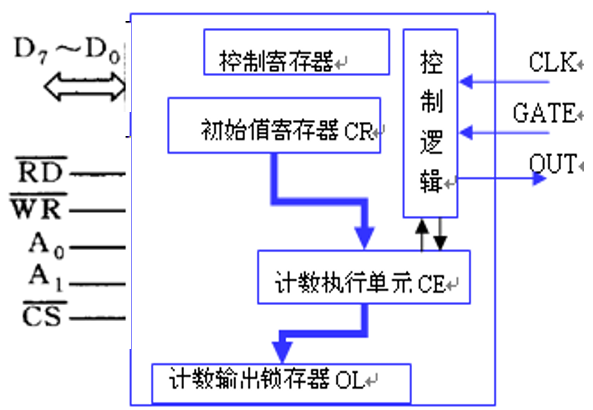

初值寄存器CR:设定计数初值

计数执行单元CE:执行计数操作,CPU不能访问

计数输出锁存器OL:CPU从中读取当前计数值

控制寄存器:决定82C54工作方式

CLK:CPU时钟信号信号

GATE:门控信号,控制83C54是否工作

OUT:输出端

注:寄存器都是16位的,但因为数据线只有8位,所以一次只能读写8位数据。

工作原理:

对CLK信号进行减1计数

1、将控制字写入控制寄存器,确定82C54工作方式

2、将计数初始值写入初值寄存器。

3、从计数初值开始,在GATE控制下,每当CLK信号出现一次,计数值减1。

4、当计数值减到0,从OUT端输出规定的信号。

注:CLK信号出现时,计数器是否减1,由门控信号GATE控制定时计数接口82C54

82C54具有三个独立的16位计数器(0#~2#通道),每个通道就是一个独立的可编程定时计数器。

每个通道有6种工作方式;

可以进行二进制或十进制计数,计数方式为减1计数。

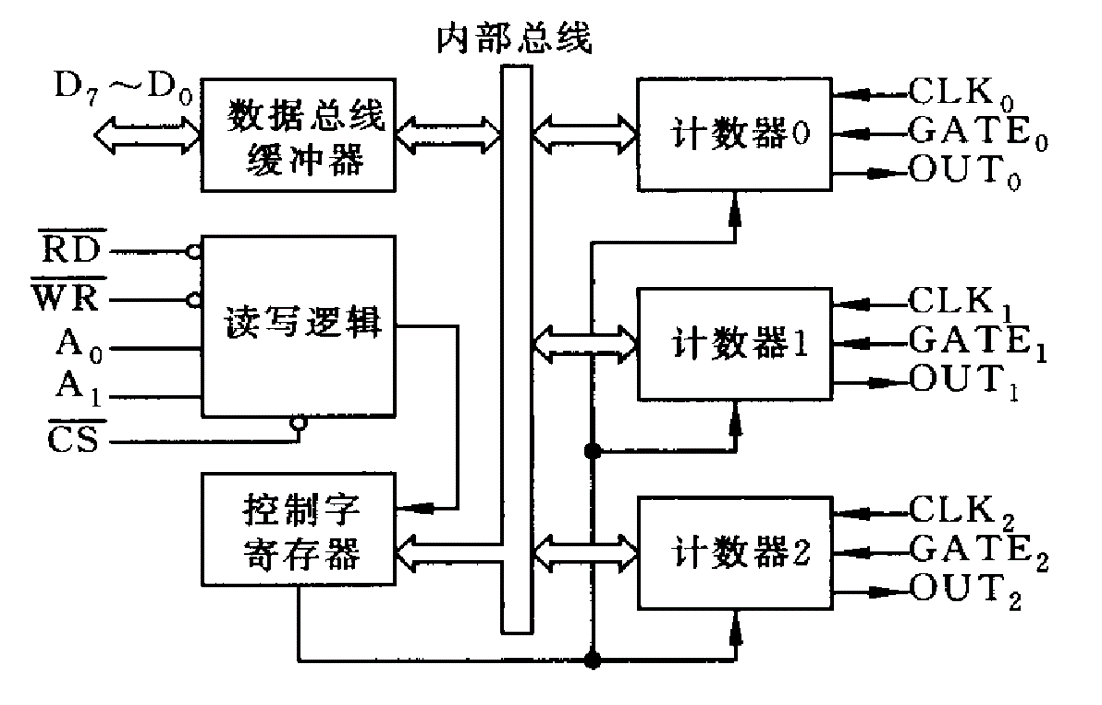

注:82C54、8254、8253都是一个意思82C54内部结构

- 数据总线缓冲器:

8位,双向,用于暂存数据。

1、初始化时向其写入控制字;

2、向某一通道写入计数初值;

3、从某一通道读当前计数初值。 - 控制逻辑:

接收CPU发来的RD、WR、CS、A1、A0信号,经过逻辑控制电路产生出对82C54要执行的操作。 - 控制字寄存器:

接收8位的方式命令字(控制字)

- 数据总线缓冲器:

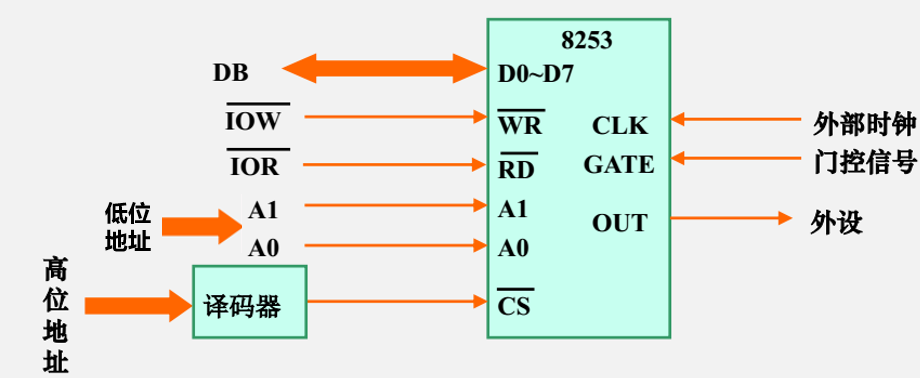

82C54外部引脚

\(\small \rm \textbf{D0}\cdots \textbf{D7}\):双向,8位数据线

\(\small \rm \overline{\textbf{WR}}\):输入,写信号

\(\small \rm \overline{\textbf{RD}}\):输入,读信号

\(\small \rm \overline{\textbf{CS}}\):输入,接口片选信号

\(\small \rm \textbf{A0 A1}\):输入,片内地址选择00:通道001:通道110:通道211:方式命令字

\(\small \rm \textbf{OUT}\):输出信号

82C54初始化编程

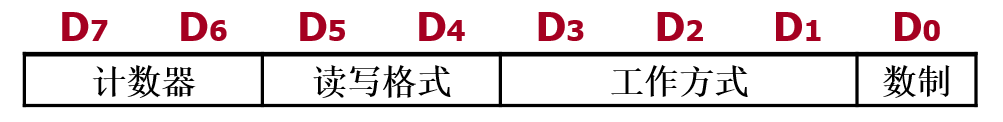

方式命令字格式

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17D7 D6:控制字是针对哪个计数器的

00:计数器0

01:计数器1

10:计数器2

11:非法。

D5 D4:设置读写格式,由计数初值的位数决定,8位-01,16位-11。

00:计数器锁存命令

01:只读写低字节

10:只读写高字节

11:先读写低字节,后读写高字节。

D3 D2 D1:指定82C54的工作模式

000:方式0

...

101:方式5。

D0:指定计数模式

0:二进制

1:十进制,即BCD码,将每个十进制位转化为4位二进制,求和还是按十进制来算。编程流程

原则: 先写方式命令字、再写计数初值。1

2

3

4

5

6

7

8

9

10

11

12

13;端口地址为60H~63H,选择1#,工作方式2,计数初值33H,BCD码制。初始化程序段为:

MOV AL,01010101B ;写入方式命令字

OUT 63H,AL ;片内地址为11

MOV AL,33H ;写入计数初值

OUT 61H,AL ;片内地址为01(使用1号通道)

;若计数初值为5533H,其他不变,则程序段为:

MOV AL,01110101B ;写入控制命令字

OUT 63H,AL

MOV AL,33H ;写入计数初值低字节

OUT 61H,AL

MOV AL,55H ;写入计数初值高字节

OUT 61H,AL

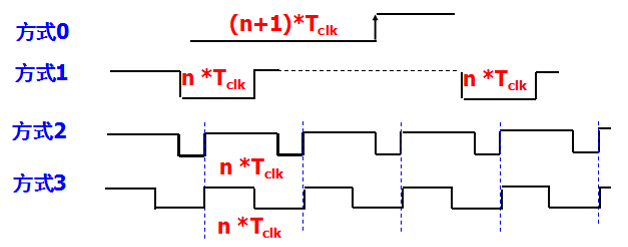

82C54六种工作方式

方式0:计数结束产生中断

方式1:可重复编程的单脉冲

方式2:分频器

方式3:方波发生器

方式4:软件触发的选通信号发生器

方式5:硬件触发的选通信号发生器

重点是方式2和方式3

6种方式不同之处

启动计数的触发方式不同。

门控信号GATE对计数操作控制不同。

是否有初值重装功能。

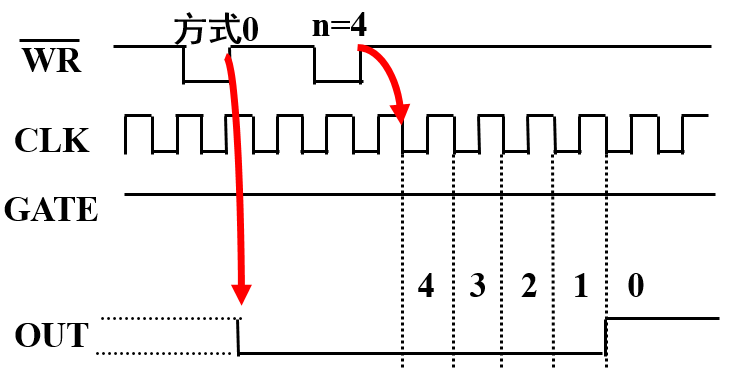

OUT引脚输出波形不同方式0(计数结束产生中断)

触发方式:软启动。写入控制字后,立即启动,OUT->低电平,但写入初值后才开始计数。

注:写入初值后要等下一个clk才开始计数,一低一高算一个clk。

GATE信号:高电平时计数,低电平时暂停计数。

初值重装:不具有

OUT波形:只计数一次,计数时为低电平,计数结束输出持续的高电平,在写入初值\((n+1)\cdot T_{clk}\)时间后发生0到1跳变。方式1(可重复编程的单脉冲)

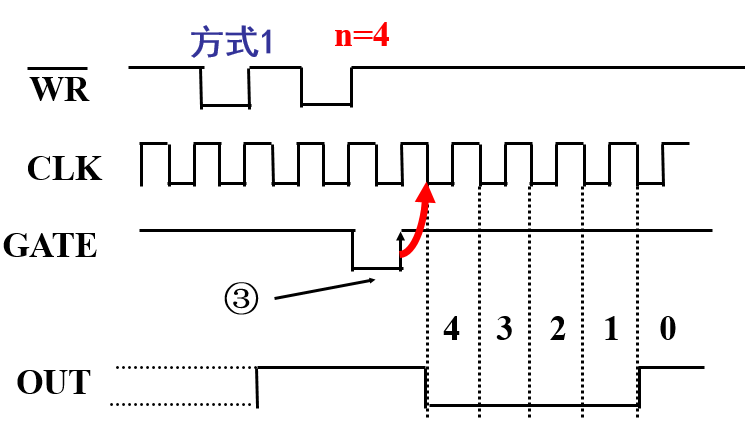

触发方式:硬件启动,写入控制字后,OUT->高电平;检测到GATE上升沿,OUT->低电平,开始计数。

GATE信号:可重复触发计数,检测到GATE上升后就重新计数。

初值重装:不具有。

OUT波形:宽度为\(n\cdot T_{clk}\)的负脉冲。

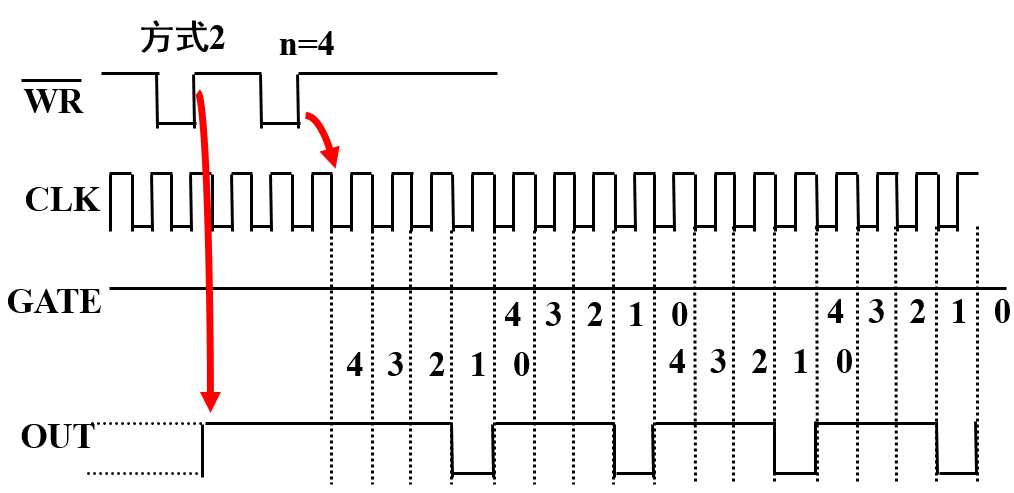

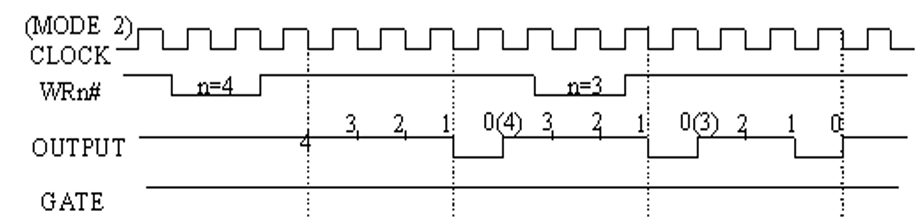

用途:单脉冲发生器,宽度由程序设置的n决定。方式2 周期性负脉冲输出(分频器)

触发方式:写入控制字后,OUT->高电平,但写入初值后才开始计数。

GATE信号:高电平时计数,低电平时暂停计数。

初值重装:具有,在计数过程中若重新写入计数初值,对正在进行的计数过程没有影响,但在计到1输出一个CLK宽度的负脉冲后,计数器将按新的计数初值开始计数。

OUT波形:产生连续的负脉冲,宽度为\(T_{clk}\),周期为\(n\cdot T_{clk}\)。

用途:分频器,放大\(T_{clk} \rightarrow n\cdot T_{clk}\),可用来提供周期性脉冲信号/时终信号。

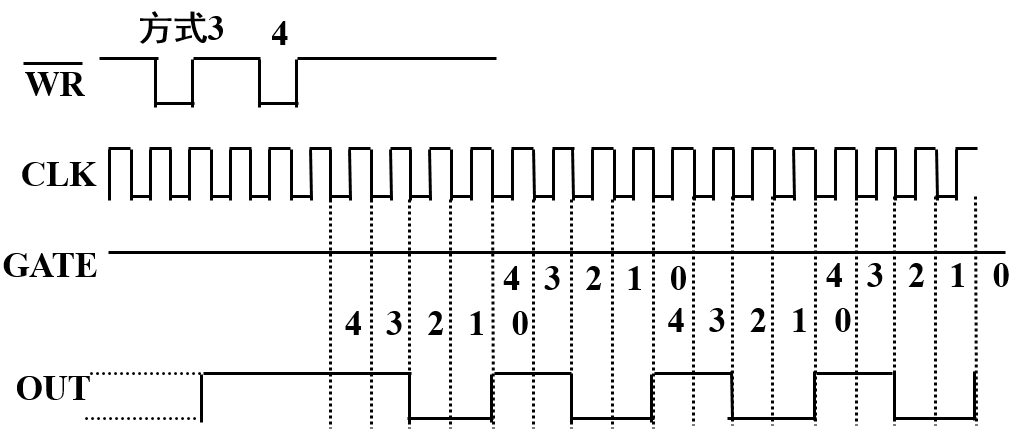

注:分频器意思是高频->低频就行,波形不一定要相同。方式3 方波发生器

(和方式2类似,只不过输出的是方波)

触发方式:写入控制字后,OUT->高电平,但写入初值后才开始计数。

GATE信号:高电平时计数,低电平时暂停计数。

初值重装:具有,和方式2原理一样。

OUT波形:产生连续的负脉冲,宽度为\(\frac {n} {2}\cdot T_{clk}\),周期为\(n\cdot T_{clk}\)。

注:当n是奇数时,输出不对称方波,前\(\frac {n+1} {2}\)个计数期间,OUT输出高电平;后\(\frac {n-1} {2}\)个计数期间,OUT输出低电平。

用途:方波发生器,也可分频。

第四章 并行接口

串/并接口指接口和外设间的连线是单根还是多根,接口和CPU间肯定是多根线。

- 并行接口特点

通过多根信号线同时传送多位数据,且传送时一般不需要特定的数据传送格式;

并行接口多用于距离短,数据量大,速率高的实时传输场合;

并行接口布线成本高,且有线路间互相干扰、时钟同步等问题,因此并行传输技术发展受限。

常用并行接口:

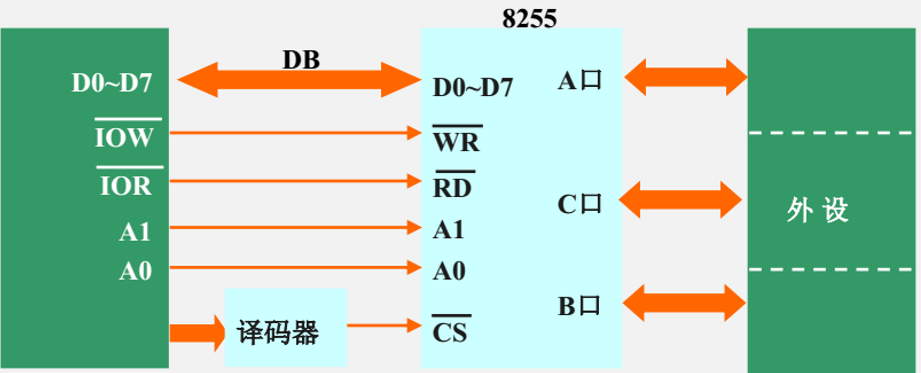

可编程并行接口8255

上一章介绍的82C54属于非通道接口,其主要功能为驱动外设,而非在CPU和外设间传数据;

本章介绍的8255是通道接口,主要功能就是在CPU和外设间传数据。

8255特点

有三个输入输出端口:端口A,端口B,端口C。

每个端口可编程设定为输入端口或输出端口,并可设定不同的工作方式。

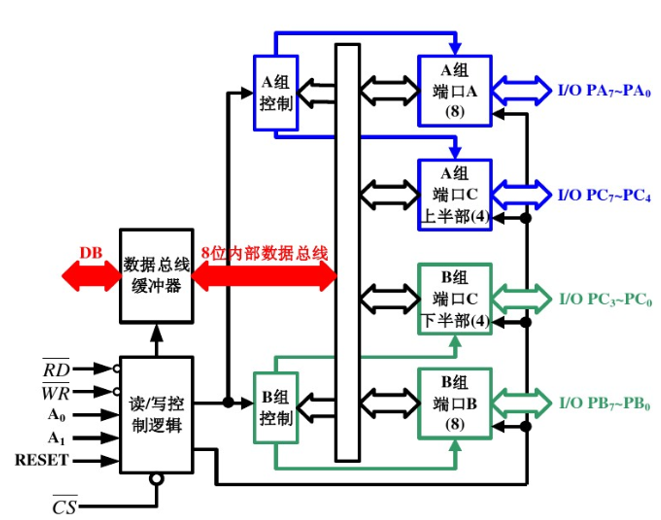

端口C可作为一个独立的端口使用,但常常是配合A口和B口工作,为A、B端口的提供联络信号。8255的内部结构

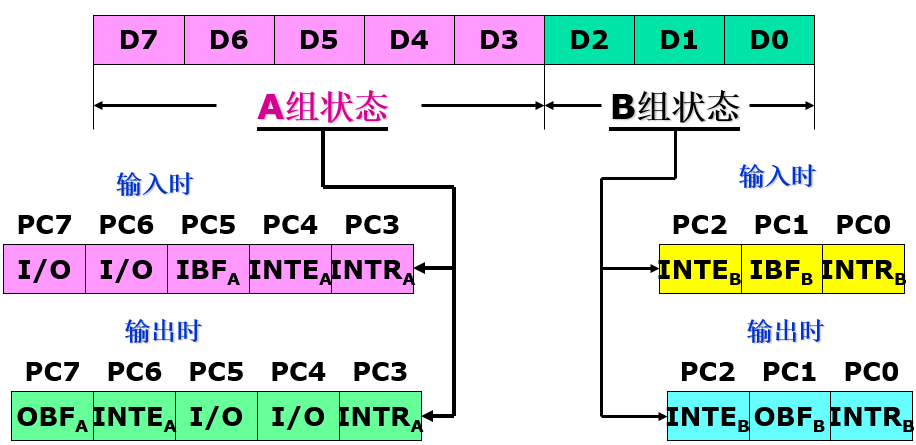

三个并行输入输出端口(A口、B口、C口)分为两组进行控制,分别对应一个控制寄存器:

A组:A口、C口高4位

B组:B口、C口低4位8255的外部引脚

片选地址A1 A0:00:A端口01:B端口10:C端口11:方式命令字

8255初始化编程

8255A有两个控制字(方式命令字,C口按位复位/置位命令字)和一个状态字,设置方法也不同。

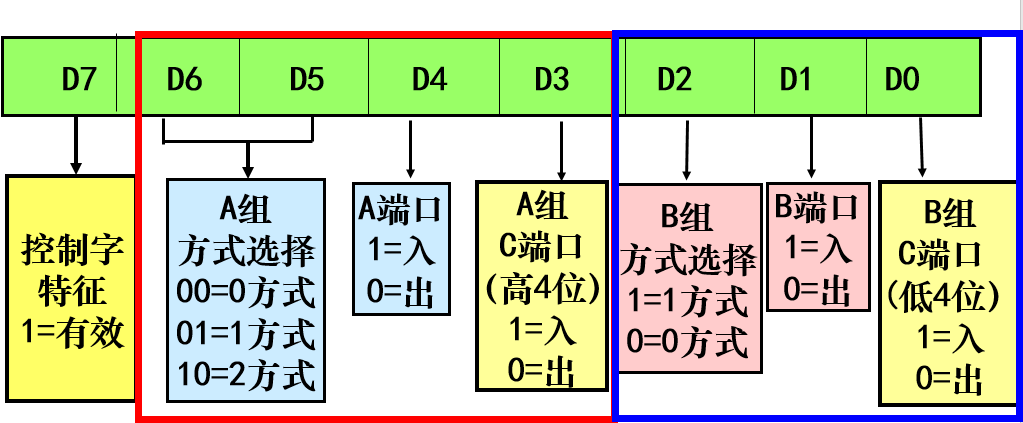

方式命令字

D7:1时表示方式命令字,0时表示C口按位复位/置位命令字

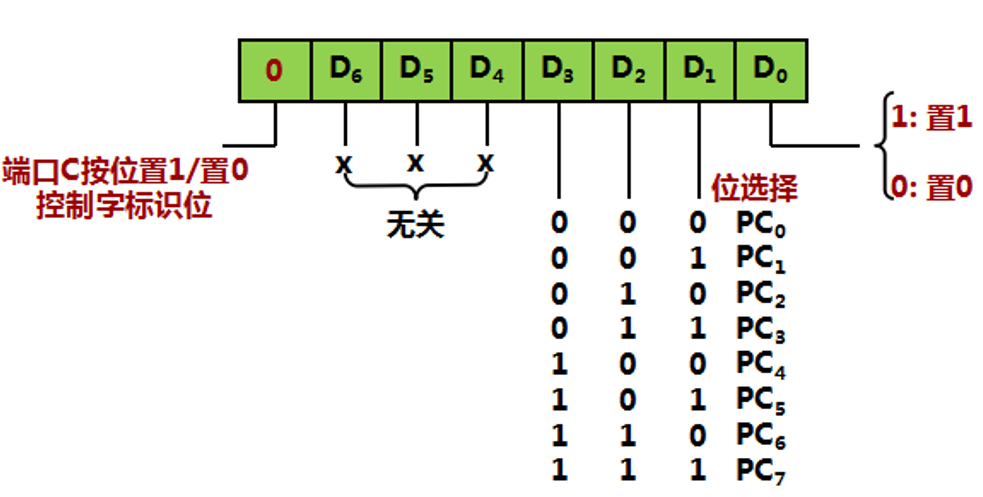

其余位按A、B组分为两组,进行不同的控制。C口按位复位/置位命令字

在方式1和方式2时要用到这个控制字,对C口的某一位置1/0,输出正/负脉冲。

此控制字只对C口有效。

它被写入控制口,不是写入C口。

编程流程

和82C54编程原则相同:先写控制字,再写数据值。

8255工作方式

8255有3种工作方式:方式0,方式1和方式2,

方式0:无条件传送(外设始终做好了准备)

方式1:单向应答式传送(查询、中断)

方式2:双向应答式传送(查询、中断)

重要是方式0和方式1

8255三个端口对工作方式的使用情况不同。

A端口:可使用3种方式的任一种;

B端口:只能使用方式0和方式1;

C瑞口:一般作为控制信号使用,配合A端口和B端口的工作。

方式0

最简单的连接方式,直接读写数据即可。

2个8位的端口和2个4位的端口,都可以作为输入或输出。

单向I/0,端口只能做输入或输出一项功能。

系统没有指定C口的某些线作为专门的信号联络线和状态位,但是用户可以自定义C口的某些线作为信号联络线。

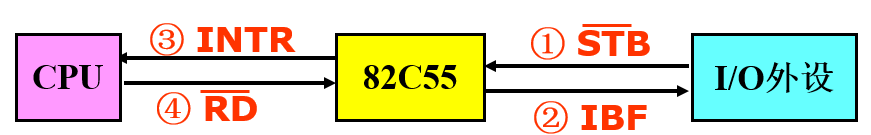

端口信号线之间无固定的时序关系,由用户根据数据传送的要求决定输入输出的操作过程。不需要任何选通信号。方式1(输入过程)

各信号意义:

\(\small \rm \overline{STB}\):选通信号,表示外设已经准备好数据。

IBF:输入缓冲器满信号,表示端口已经接收数据完毕。

INTR:中断请求信号,请求CPU接收数据。

\(\small \rm \overline{RD}\):读数据信号,有效代表CPU在读取数据。在外设向CPU发出INTR信号后,什么时候CPU响应了中断,\(\small \rm \overline{RD}\)即变为有效。.png)

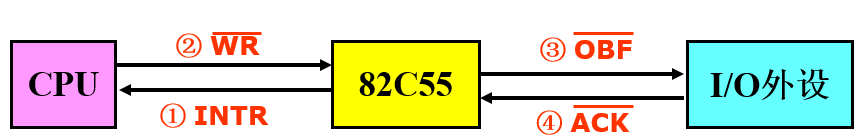

方式1(输出过程)

各信号意义:

INTR:中断请求信号,接口向CPU发出中断。

\(\small \rm \overline{WR}\):写信号,表示CPU向接口在写数据。

\(\small \rm \overline{OBF}\):输出缓冲器满信号,表示外设可以从接口中取数据了 。

\(\small \rm \overline{ACK}\):外设应答信号,\(\small \rm \overline{ACK}=0\)其实是一个负脉冲,表示外设已接收完数据,可以再发下一个数据,因此马上会回到高电平。.png)

CPU响应中断以后,向8255输出数据,写信号出现;写信号撤消,其上升沿一方面撤消中断请求信号INTR,另一方面使\(\small \rm \overline{OBF}\)信号变为有效的低电平,通知外设可以接收数据。

当外设接收完数据后,便发出一个\(\small \rm \overline{ACK}\)信号,同时使\(\small \rm \overline{OBF}\)变为无效,表示数据已经取走,当前缓冲器空。\(\small \rm \overline{ACK}\)信号结束时使INTR信号变为有效的高电平,向CPU发出中断请求信号,从而开始新的数据输出过程。方式1下的C口状态字

INTE:中断使能状态,表示是否允许端口发出INTR信号。初始化时通过C口按位复位/置位命令字来设定,设定后,就会在状态字中反映出来。

PC0-PC7:指C口的对应位,为A口和B口的提供辅助信号。A组:8位数据口+5位控制口(PC3-PC7),B组:8位数据口+3位控制口(PC0-PC2)。

状态字作用:

状态字主要为查询方式提供了状态标志位,方式1下,CPU读取的C口某几位内容,主要有:\(\small \rm \overline{OBF}\)、IBF、INTE、INTR,来判断下一步应该进行的操作。

注1:A口、B口都有相应的状态字,实质是相互独立的两个数据口。

注2:\(\small \rm \overline{STB}\)、\(\small \rm \overline{ACK}\)线的状态不能读取,因为是来自外设的信号,所以状态字中没有,CPU也不需要知道。

注3:端口C状态字寄存器的值和对应的引脚信号不一定一样。如输入状态下,PC4寄存器值表示INTE,而引脚则接\(\small \rm \overline{STB}\)信号。因为INTE是在初始化时设置的,而\(\small \rm \overline{STB}\)信号又不写到寄存器中,所以两者并不冲突,这样可以提升端口利用率。

第五章 中断技术

中断的基本概念

中断的本质是程序转移:CPU响应中断请求,暂停现行的主程序,转去执行中断服务子程序,完成中断事件处理后,返回断点继续执行主程序的过程。

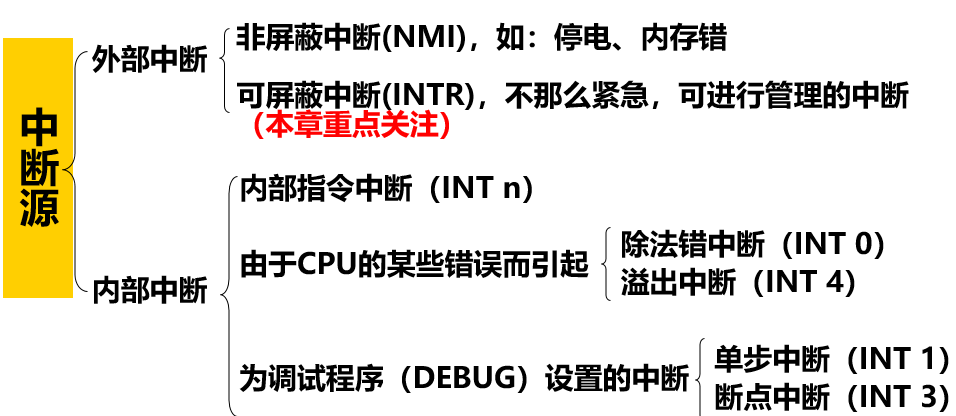

中断的分类

中断的内、外是针对CPU而言的,外部中断即来自CPU外部的中断。外部可屏蔽中断的一般流程

1、中断请求:INTR,请求信号应保持到本次中断被响应

2、中断识别及判优:通过类型号区分不同中断源,通过优先级进行中断判优

3、中断响应:保护现场等操作(硬件完成)

4、中断处理:执行中断服务子程序

5、中断返回:恢复现场等操作(硬件完成)中断向量与中断向量表

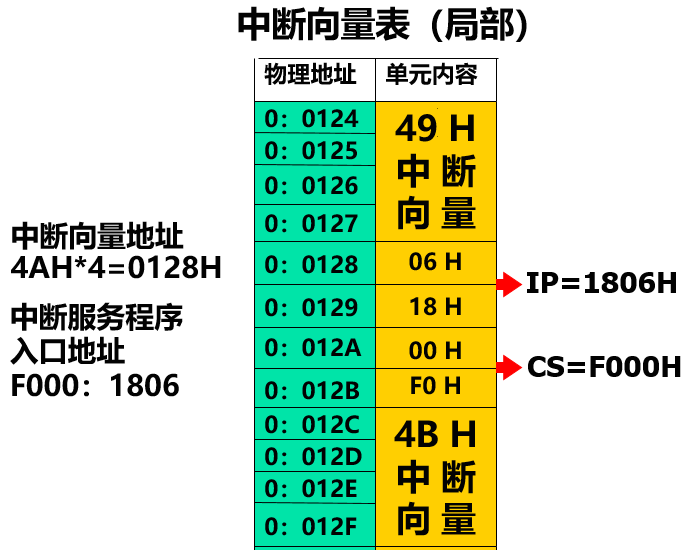

中断类型号:8086微处理器支持256种中断,编号为0~255号。

中断向量:中断服务程序的入口地址,CS:IP的形式存储,占4个字节的地址。

中断向量表:系统中所有的中断向量集中起来放到存储器的某一区域内,即为中断向量表。在内存中用000~3FFH共1024(4*256)个地址作为中断向量表存储区。

由中断号计算中断服务程序地址:先计算中断向量的地址(4*中断号),再取出中断服务程序的地址。总共四个字节,低2字节为IP,高2字节为CS,都是小端存储。

eg:计算中断类型号为4AH的中断服务程序入口地址

可编程中断控制器8259A

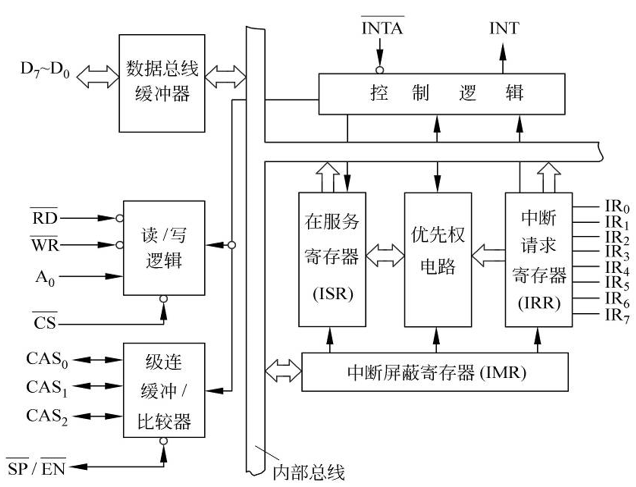

作用:接收外设传来的中断,进行中断识别和判优,并将应该响应中断的中断号传给CPU。只传中断号,并不执行中断。

8259A只是帮助系统管理外部可屏蔽中断,外部不可屏蔽中断及内部中断CPU自己处理。

8259A具有8级优先权控制,通过级连可扩展至64级优先权控制。

8259A内部结构

中断请求寄存器(IRR):该寄存器8位(D0~D7)对应于IR0~IR7线上传来的中断请求,哪一根输入线有请求,哪位就置“1”,中断被响应后对应位就置0。

中断屏蔽寄存器(IMR):寄存器8位(D0~D7)对应8级中断屏蔽,IR0~IR7哪一个中断被屏蔽,哪位就写1。

优先权分析器(PR):PR将当前中断请求的优先级和“正在服务中的中断”进行比较,决定是否让这个中断请求送给处理器(低优先级就不送了)。

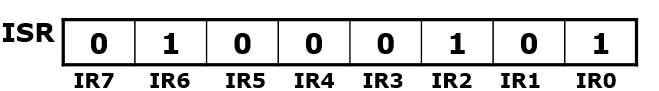

ISR寄存器:寄存了正在服务的\(\small \rm IR_{i}\)中断源和被挂起的中断源,可根据优先级规则判断哪个中断源正在被服务。

被挂起的含义:低优先级中断先响应了,之后来了高优先级中断,就挂起去执行高优先级(若高优先级先响应,低优先级压根就不会送到ISR)。

如下图:若IR0中断优先级最高,IR7优先级最低,则当前被服务的是IR0,被挂起的是IR2和IR6。

级联缓冲/比较器(CAS0~CAS2):主控和从控芯片的CAS0~CAS2相互连接,进行级联;从控的INT引脚接到主控的IR上,传递中断号。

如何区分主控和从控:SP/EN引脚接高电平为主控,接低电平为从控。8259A外部引脚

8259A中断响应过程

1、IRQ0~IRQ7有中断请求,IRR的相应位置1

2、IRR与IMR相应位进行比较,封锁或发送中断请求给PR

3、PR分析后,把当前最高优先级的中断请求由INT送至CPU

4、若IF=1,CPU执行完当前指令后,连续发出2个\(\small \rm \overline{INTA}\)信号(IF=1表示开中断)

5、接到第1个\(\small \rm \overline{INTA}\)后,ISR对应位置1,IRR对应位清0

6、接到第2个\(\small \rm \overline{INTA}\)后,8259A把中断类型号送上数据总线

7、CPU根据收到的中断类型号,到中断向量表中取中断向量,执行中断子程序。

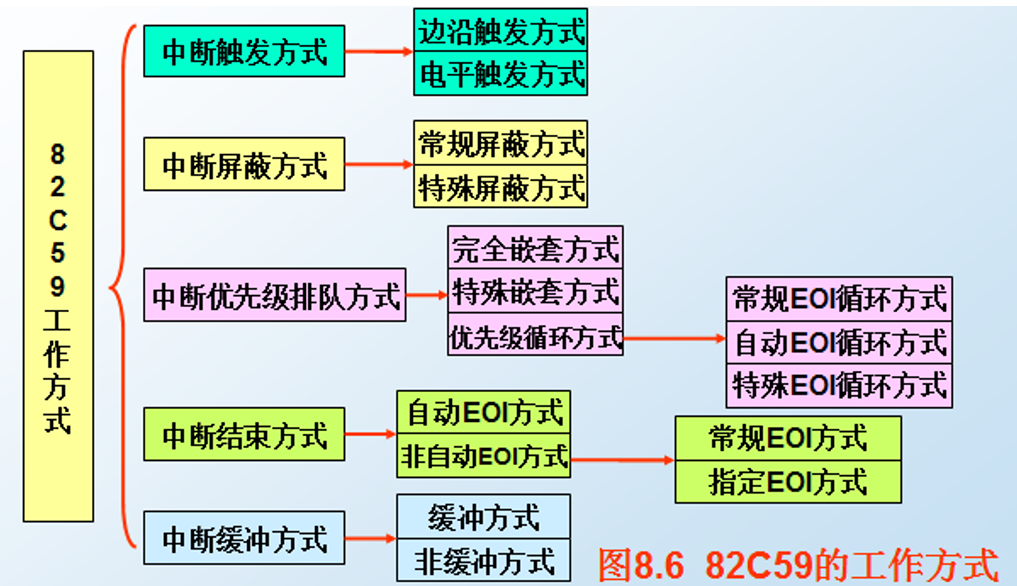

8259A工作方式

因为其他部分都不太重要,因此接下来重点介绍优先级排队方式。

普通完全嵌套方式

在该方式下,IR7~IR0的优先级顺序是IR0最高,IR7最低。且一个中断被响应,只有比它更高优先级的中断请求才会被响应。特殊嵌套方式

该方式一般用于8259A的级联方式

与全嵌套方式基本相同,不同之处在于特殊嵌套不但响应比本级高的中断申请,而且响应同级的中断申请。

如果当前正在执行的中断是由从片传来的,这是从片上更高级别的中断提出请求,从片会予以响应,向主片发INT信号,但主片分不出来,只将它们视为同一级别。

若普通全嵌套方式,则主片不会响应,只有特殊全嵌套方式,主片才会响应。因此级联时主片必须采取特殊嵌套方式。优先级循环方式

指当某个中断源受到中断服务后,它的优先权就自动降为最低,而优先级较其低一级的升为最高。

例如,IR4被服务后,相应的IR5的优先级升为最高,依次为IR6,IR7,IR0,IR1,IR2,IR3,IR4。

根据初始优先级的不同又分为两种方式:

普通循环方式:默认初始优先级最高为IR0,最低为IR7。

特殊循环方式:用户自己决定初始优先级,如规定IR5最低,则相应的最高优先级为IR6,依次为IR7,IR0,IR1,IR2,IR3,IR4,IR5。

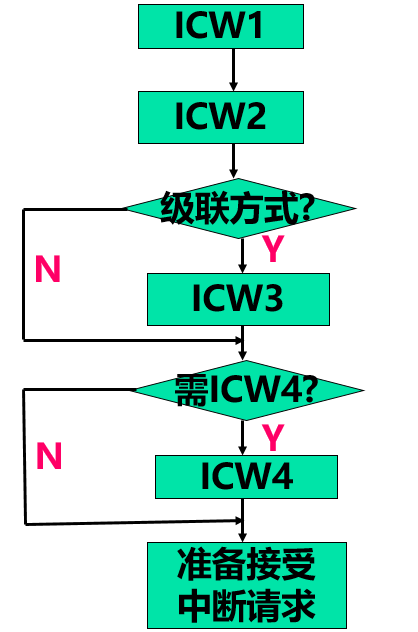

8259A初始化命令字

8259A有4个初始化命令字ICW1~ICW4,在接口使用前进行设置。

初始化命令字必须按ICW1~ICW4的顺序写入,中间不能被打断(关中断)。且ICW1、ICW2是必须写的,ICW3、ICW4需不需要写视工作方式而定。

写入地址:ICW1要写到偶地址(A0=0),ICW2~ICW4写到奇地址(A0=1)。

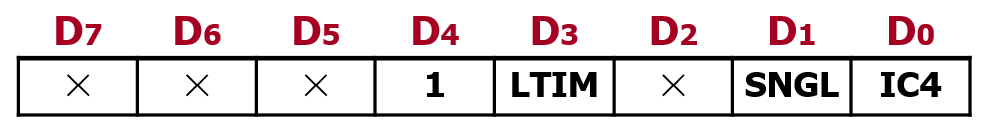

ICW1(芯片控制命令字)

1

2

3

4

5

6

7

8

9

10

11

12D7 D6 D5:可任意设置,建议设为0

D4:标志位,只能设为1

D3:设置中断触发方式

1:电平触发方式

0:边沿触发方式

D2:任意设置,建议为0

D1:规定单片还是级连方式

1:单片方式

0:级连方式

D0:是否写入ICW4

1:要写入ICW4

0:不写入ICW4ICW2(中断类型号命令字)

1

2

3

4D7~D3:设置中断向量号的高5位,手动设置。

D2~D0:中断向量号的低3位,8259A会自动确定。

IR0为000、IR1为001...IR7为111

写的时候只用写D7~D3即可,D2~D0自动设为0。

最终中断号=ICW2的高5位+\(\small \rm IR_{i}\)组合而成。

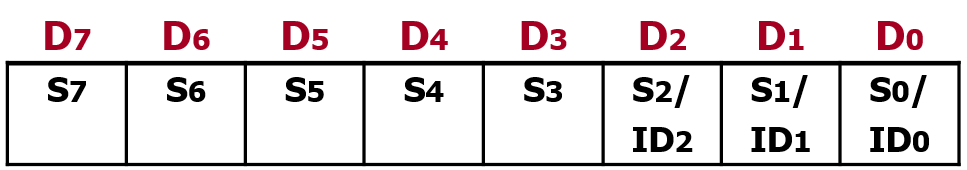

ICW3(级联控制命令字)

ICW3是级联时才需写入的控制字,且对于主、从片的意义不同。1

2

3

4

5

6

7

8

9

10对于主片:Di=1表示IRi接有从片,否则IRi没有接从片。

对于从片:D2~D0表明从片的INT引脚接到主片的哪个IR引脚。

例:主控8259第IR3、IR6上联了从控。

主控:ICW3=01001000B,

从控A:ICW3=00000011B,

从控B:ICW3=00000110B。

如何区分主控和从控:SP/EN接高电平为主控,接低电平为从控。

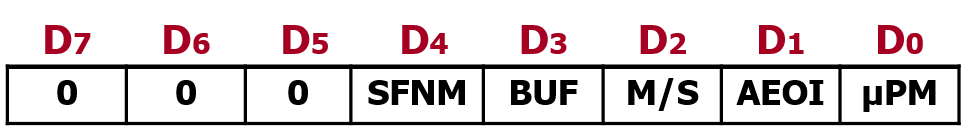

主控和从控的CAS0~CAS2相互连接,进行级联;从控的INT引脚接到主控的IR上,传递中断号。ICW4(方式命令控制字)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16D7 D6 D5:直接设0

D4:设置嵌套方式

1:特殊嵌套方式

0:普通完全嵌套方式

D3:数据线的缓冲方式

1:缓冲方式

0:非缓冲方式

D2:主片/从片选择

1:主片

0:从片

D1:中断结束方式

1:自动中断结束

0:非自动中断结束

D0:微处理器类型

1:16位80x86

0:8位8080/80858259A初始化流程

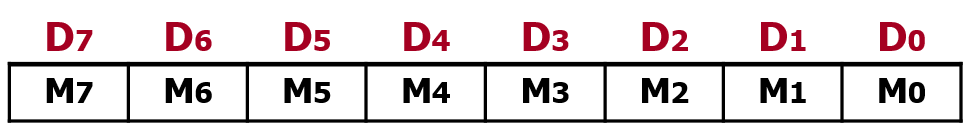

8259A操作命令字

8259A有3个操作命令字OCW1~OCW3,负责对8259A的工作状态进行设置。

在8259A工作期间,可以随时接受操作命令字,且对写入顺序没有要求,需要哪个OCW就写入那个OCW。

写入地址:OCW1写到奇地址(A0=1),OCW2、OCW3写到偶地址(A0=0)

OCW1(屏蔽命令字)

内容写入中断屏蔽寄存器IMR,\(\small \rm D_i\)对应\(\small \rm IR_i\)1:禁止\(\small \rm IR_i\)中断0:允许\(\small \rm IR_i\)中断OCW2

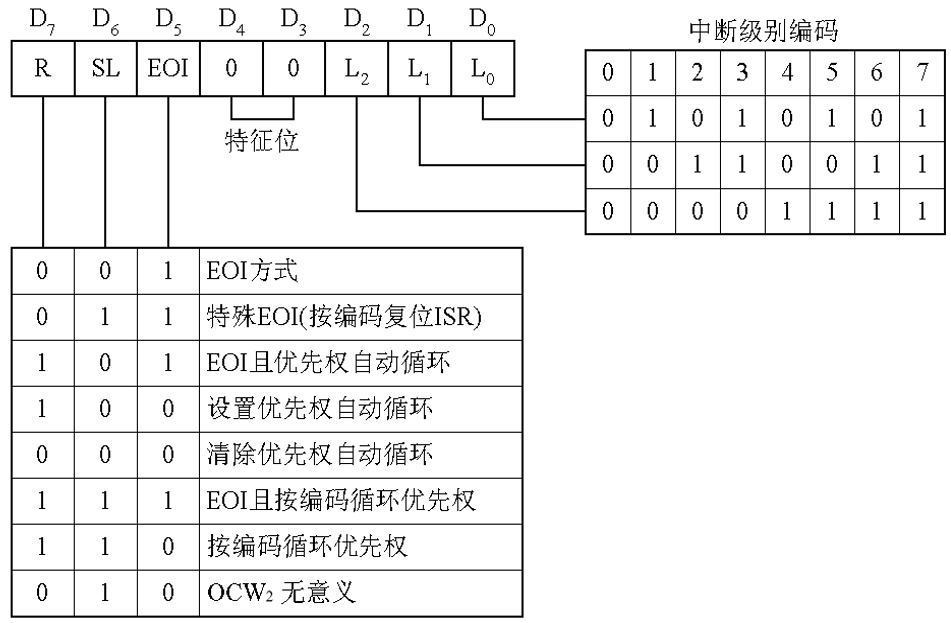

OCW2用于设置优先级循环方式和中断结束方式1

2

3

4

5

6

7

8

9

10

11D7 D6 D5:组合为设置编码

D7:是否允许优先权循环

D6:设置优先级方式

1:循环优先级(按D2~D0决定哪个引脚优先级最低)

0:固定优先级(IR7最低,IR0最高)

D5:是否允许EOI,EOI:结束中断,结束D2~D0对应引脚的中断

1:允许

0:不允许

D2 D1 D0:指定优先级循环时,初始的最低优先级的引脚

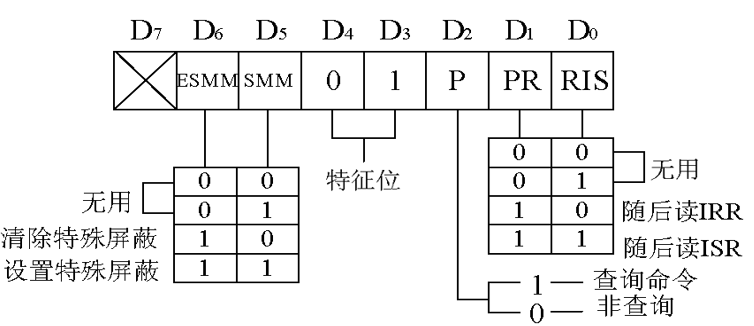

eg:D2~D0为101,表明指定初始时最低优先级为IR5,则最高优先级为IR6。OCW3

OCW3用于设置和撤消特殊屏蔽方式、设置中断查询方式以及发出对8259A内部寄存器的读出命令。如何区分初始化命令字和方式命令字

8259A只有两个端口用来写命令字(一个奇地址一个偶地址),如何区分写到地址中的命令字?

对于奇地址:ICW1、OCW2、OCW3都写到奇地址,通过命令字的D4 D3两位来区分。

对于偶地址:ICW2~4、OCW1都写到偶地址,通过写入顺序来区分,系统规定只能按ICW2->ICW3->ICW4->OCW1的顺序写入。

第六章 A/D、D/A转换器接口

在实际工业生产环境,都是连续变化的模拟量 ,如:压力、温度、流量等;

而在计算机内部,则都是离散的数字量,二进制数、十进制数、十六进制等。

因此需要对连续的模拟量和离散的数字量做转换,就出现了A/D(Analog to Digital)、D/A(Digital to Analog)转换器芯片。

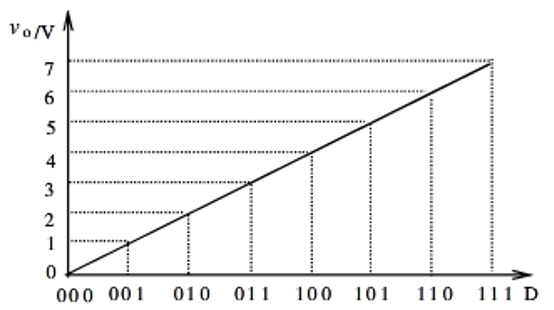

D/A转换芯片DAC0832

D/A转换器的功能是把二进制数字量电信号–>与其数值成正比的模拟量电信号(电压、电流..)。

如下图:横坐标为输入的数字信号量,纵坐标为输出的模拟信号量。

DAC0832主要有三项技术指标:分辨率、精度和建立时间。

分辨率

分辨率是指输入数字量发生一个单位的变化时,输出模拟量的变化量,这个参数反映了DAC对模拟量的分辨能力

eg:

满刻度值电压为5V、10位DAC:能分辨的电压为\(\small 5/2^{10}=4.88(mV)\)。

满刻度值电压为5V、8位DAC:能分辨的电压为\(\small 5/2^8=19.53(mV)\)。精度

精度表明了模拟输出实际值与理想值之间的偏差,可能工艺做的器件比较粗糙,导致实际用的时候有误差,反映的是“工艺”精度。建立时间

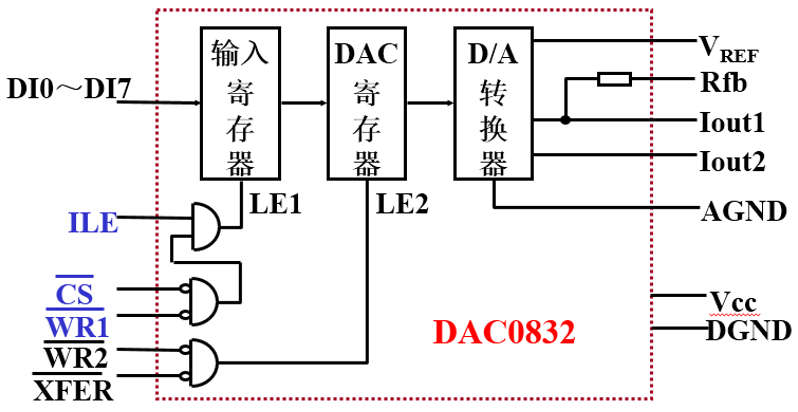

从数字输入端发生变化开始,到模拟输出稳定在理想值的\(\pm \frac{1} {2}\)\(\small LSB\)时所需的时间(LSB指分辨率)。DAC0832内部结构

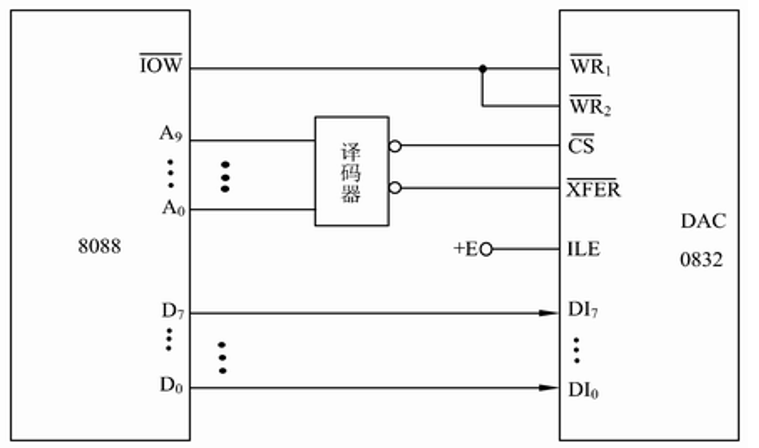

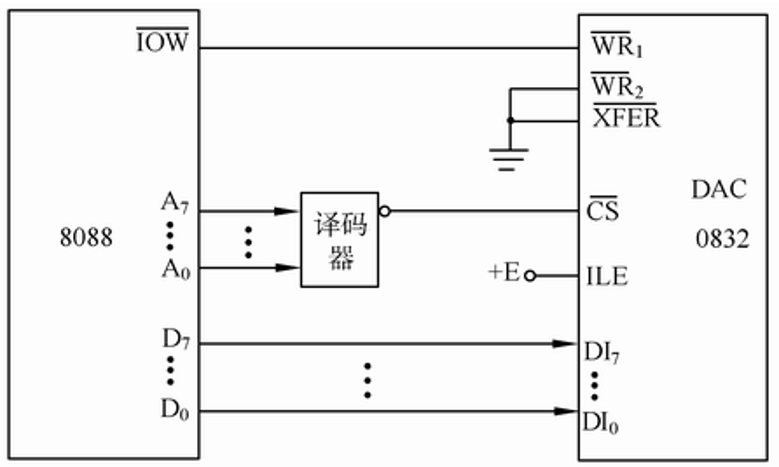

DAC0832内部有两个数据缓冲器,分别由两组控制信号控制:

输入寄存器:存放外部输入的数据,当\(\small ILE=1\cap \overline{CS}=0\cap \overline{WR1}=0\)时,\(\small LE1\)端有效,DI7~DI0上的数据锁被写到输入寄存器中。

DAC寄存器:存放要输出的数据(D/A转换器根据DAC寄存器中的值计算输出的模拟值),当\(\small \overline{XFER}=0\cap \overline{WR2}=0\)时,\(\small LE2\)端有效,输入寄存器中的数据被写到DAC寄存器中。

DAC0832外部引脚:

\(\small DI0\sim DI7\):8位数字输入端,DI0为最低端,DI7为最高端。

\(\small ILE\):数据输入锁存允许,通常一直为高电平;

\(\small \overline{CS}\):片选信号1–>输入寄存器。

\(\small \overline{XFER}\):片选信号2–>DAC寄存器。

\(\small \overline{WR1}\):写信号1,输入寄存器写选通信号。

\(\small \overline{WR2}\):写信号2,DAC寄存器写选通信号。

\(\small Iout1\):DAC电流输出端1,为数字输入端为1的位的输出电流之和。全1时最大,全0时最小。

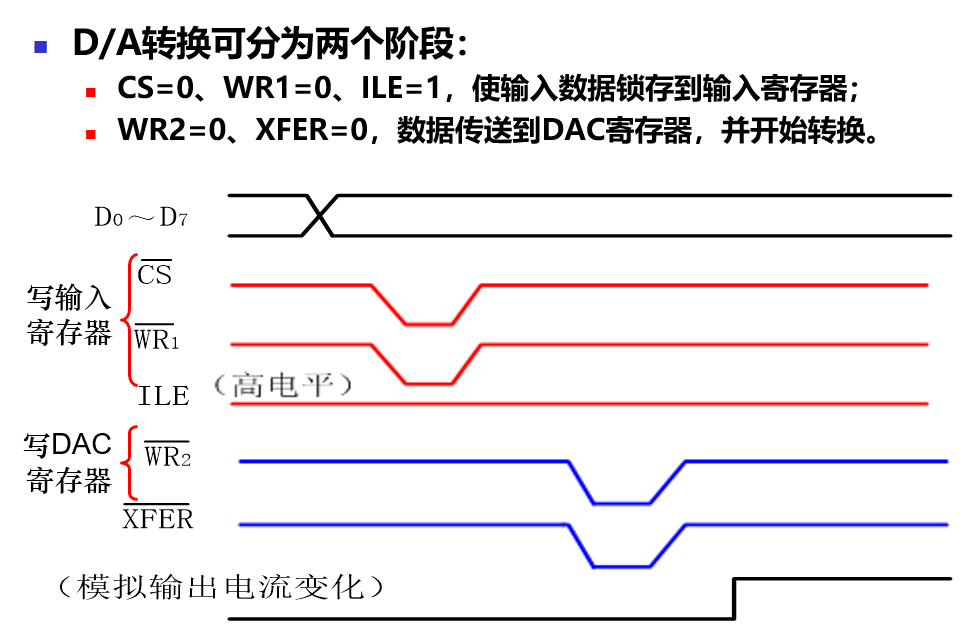

\(\small Iout2\):电流输出端2,\(\small Iout1+Iout2=常数\)DAC0832工作时序

DAC0832工作方式

DAC0832没有应答信号,有数据输入时,若已经选通了,即开始转换;也没有控制字信号,直接送数据即可。

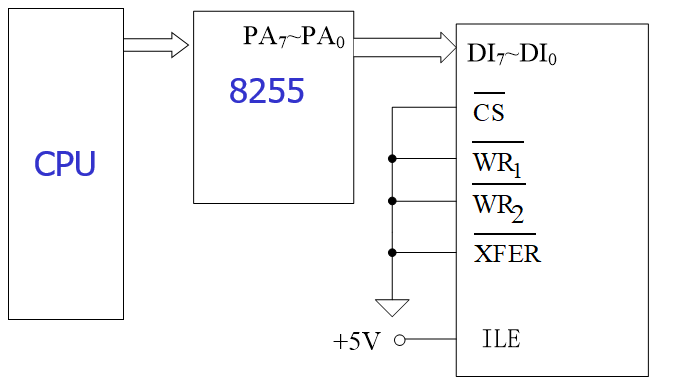

DAC0832有单缓冲模式、双缓冲模式、无缓冲模式三种工作方式,重点是单缓冲模式。

缓冲的含义:缓冲即指锁存,锁存就是寄存器能否暂存数据(尽管有新的输入数据,但仍旧保持原有的值,直到某个信号的到来才更新寄存器的值)。如果没有锁存功能,就是寄存器值和输入值保持同步,输出会随着输入而变化。

在DAC0832中,实现两个寄存器的缓冲功能,要通过寄存器对应的选通信号线:选通信号线处于无效状态,数据就写不进去,就实现了缓冲/锁存。若选通信号线恒有效,就没有缓冲功能。

如何设置工作方式:0832没有命令字,根据选通信号引脚连线的不同来决定工作方式。

双缓冲方式

输入寄存器、DAC寄存器都有缓冲功能。当把数据由输入寄存器写到DAC寄存器以后,输入寄存器就可以接受新数据而不影响模拟输出值,该结构便于多路DAC同时工作(可以时分复用,利用DAC寄存器中数据转换的时间读取数据)。

1

2

3

4

5要分别对两个寄存器写数据

MOV DX,200H ;DAC0832 的输入锁存器的地址为200H

OUT DX,AL ;AL中数据DATA送输入寄存器

MOV DX,201H ;DAC0832 的DAC锁存器的地址为201H

OUT DX,AL ;数据DATA写入DAC锁存器并转换单缓冲方式

只有输入寄存器有缓冲功能。只需一次写操作,就开始转换,提高了D/A的数据吞吐量。适合在不要求多片D/A同时输出时。

1

2MOV DX,200H ;设DAC0832的地址为200H

OUT DX,AL ;AL内数据送DAC转换直通方式

两寄存器都没有缓冲功能,输出随输入同步变化。

1

2MOV DX,200H ;8255的A口地址为200H

OUT DX,AL ;AL中数据送A口锁存并转换用DAC0832输出三角波

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20;设输出初始值0

L1: MOV AL, 0

;输出数值递增,产生三角波上升沿

UP: MOV DX, 300H ;单缓冲

OUT DX, AL

INC AL

CALL DELAY

;判断输出是否为0,JNZ:不为0跳转

AND AL, AL

JNZ UP

;输出数值递减,产生三角波下降沿

DOWN: DEC AL ;AL=0-1=255

OUT DX, AL

CALL DELAY

;判断输出是否为0

AND AL, AL

JNZ DOWN

LOOP L1

A/D转换芯片ADC0809

将模拟信号转换为数字信号

A/D转换基本原理:

采样:利用采样脉冲序列,从信号中抽取一系列离散值,使之成为采样信号;

量化:把采样信号经过舍入变为只有有限个有效数字的数,使电流和数据有一一对应的关系;

编码:将经过量化的值变为二进制数字。

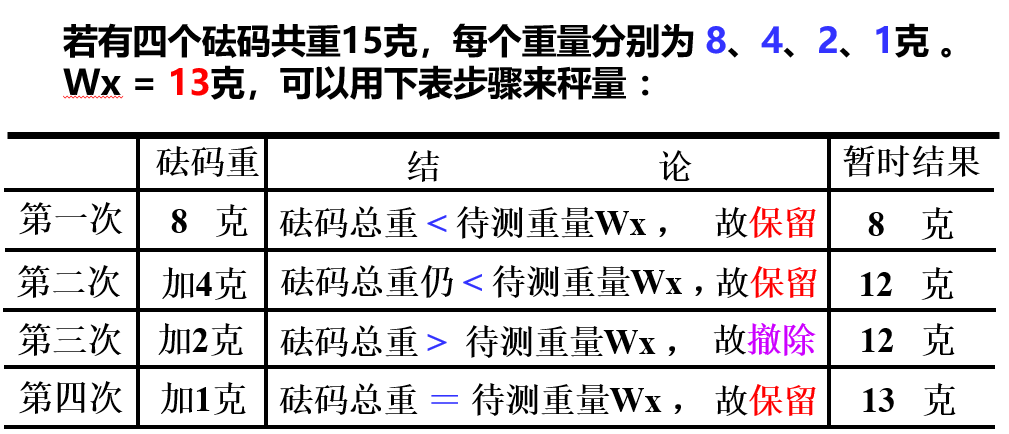

如何将十进制数值转换为二进制:使用逐次逼近的方法,具体原理如下图:

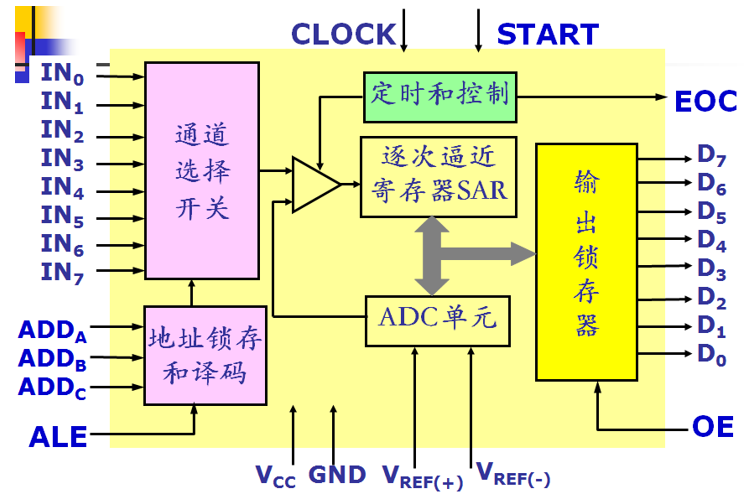

ADC0809结构

IN7~IN0:8路模拟信号输入。

ADDC、ADDB、ADDA:8路模拟信号量的地址选择线,选择要接收的一路模拟信号量。

ALE:地址锁存允许,其正跳变锁存地址选择线状态,经译码选通对应的模拟输入信号。

START:启动信号,上升沿使片内所有寄存器清零,下降沿启动A/D转换(通常与ALE共用一根线)。

EOC:AD转换结束信号,转换开始后,此引脚变为低电平,转换一结束,此引脚变为高电平;

OE:输出允许,当有效时,D7~D0输出结果。

D7~D0:8位数据输出线。ADC0809输出数据的传送方式

延时等待法:软件延时等待足够长的时间(大于转换时间),此时不用EOC信号,CPU效率最低。

中断法:把EOC作为中断请求信号,在中断服务程序中读入转换结果,效率较高。

查询法:软件查询EOC信号的状态。

具体代码见PPT

第七章 串行接口

串行通信方式基本概念

串行通信方式:在一条传输线上,将多位数据从低位到高位顺序地进行传输。

并行通信方式:在多条传输线上同时传输多位数据,且有专门的联络、控制信号线。

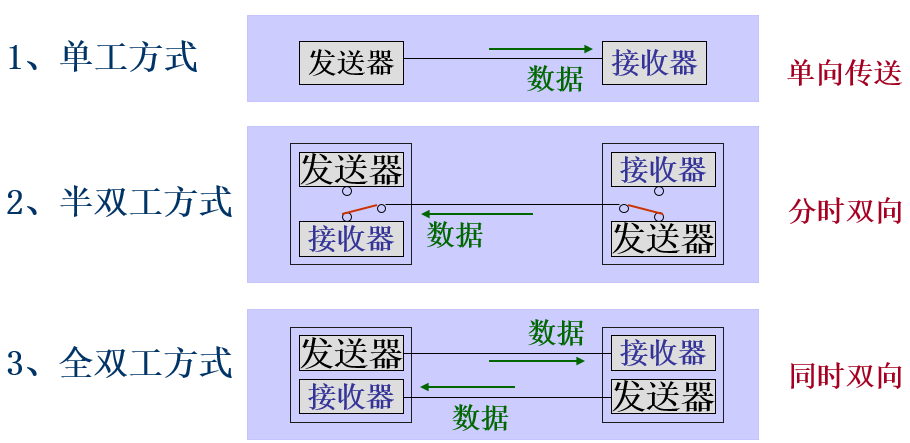

串行通信的数据传送方向

信号的调制和解调

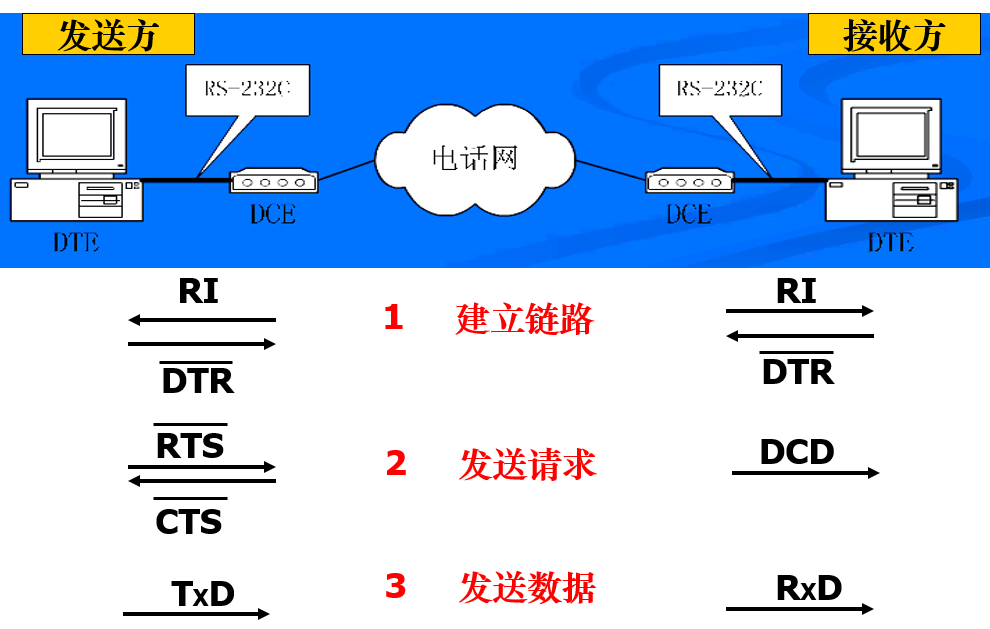

数据通信设备DCE:Modern

数据终端设备DTC:主机、终端通讯设备。

三种调制方式:振幅键控(ASK),频移键控(FSK)和相移键控(PSK)数据的传输速度

数字通信中,传输速率经常用波特率(baud)来表示。同时为提高发送/接收时钟对波特率的定位精度,发送/接收时钟的频率常定为波特率的整数倍(1、16、32、64),这个整数称为波特率因子。$$TxC=factor\times baud$$ TxC为发送/接收时钟频率。

波特率因子可理解为发送/接收1位数据所需要的时钟脉冲个数,即在发送端,需要多少个时钟脉冲才能移出1位数据。时钟脉冲多一些,可提高定位采样的精度。串行通信的基本方式

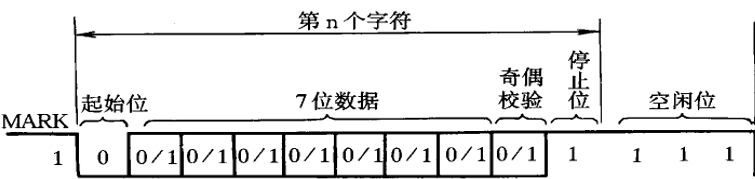

异步串行通信:以字符为单位发送数据,字符间间隔不定(异步),但字符内各位是同步的。适合数据量少、速率低,发送数据不连续的场合。

同步串行通信:以数据块为单位发送数据,字符间、字符内都是同步的。适合速率高,连续传输大批量数据的场合。

外同步:发送端发数据前先发送同步时钟信号,接收方用这一同步信号来锁定自己的时钟脉冲频率,来达到收发双方位同步的目的。

自同步法:接收方利用包含有同步信号的特殊编码(如曼彻斯特编码)从信号自身提取同步信号来锁定自己的时钟脉冲频率,达到同步目的。串行通信数据格式

对于异步串行通信,因为字符间的间隙不固定,因此要有起始位和终止位。

对于同步串行通信,要求有时钟来实现发送端与接收端之间的同步,因此有很多控制字符,因较为复杂就不列举了。

串行接口标准RS-232C

电气特性

在TxD和RxD数据上:

逻辑1(MARK) = -3 ~ -15V

逻辑0(SPACE) = +3 ~ +15V

在RTS、CTS、DSR、DTR和DCD等控制线上:

信号有效(接通,ON状态)= +3 ~ +15V

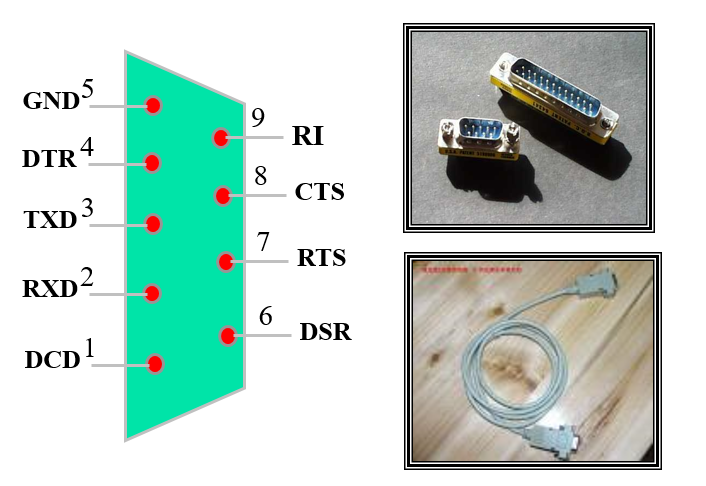

信号无效(断开,OFF状态)= -3 ~ -15VRS-232C的引脚信号线

数据发送与接收线:

TxD:发送数据,将串行数据发送到MODEM

RxD:接收数据,从MODEM接收发来的串行数据

状态线:

DSR:表明MODEM可以使用。

DTR:表明数据终端可以使用。

信号联络线(modem之间建立通信链路):

RI:振铃指示,当MODEM收到交换台送来的振铃呼叫信号时,通知终端,表示交换台准备好了。

DCD:数据载波检出线,表示MODEM已接通通信链路。

信号联络线(modem与终端之间):

RTS:请求发送,表示DTE请求DCE发送数据。

CTS:允许发送,表示DCE准备好了,DTE可以发数据,是对RTS的响应信号。

地线:

GND:地线数据传输过程

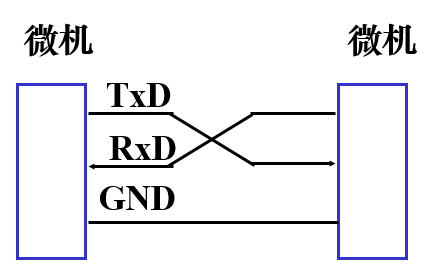

微机间连线方式

重点是不使用联络信号的3线相连方式,如下图所示:

不使用Modem,TxD和RxD要交叉连接。

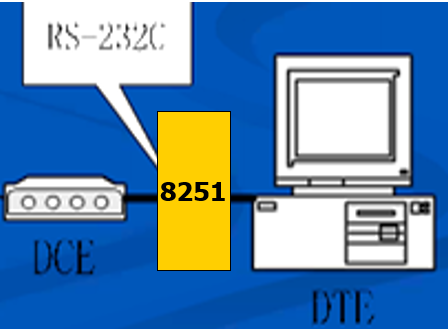

8251可编程通信接口

8251是通用同步异步接收发送器USART(Univesal Synchronous Asynchronous Receiver and Transmitter),适合作为异步起止式和同步面向字符式的接口。

第八章 存储器

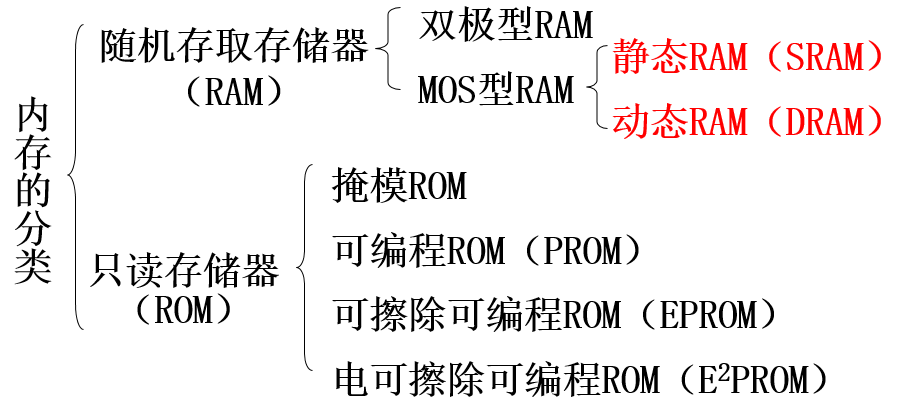

内存的分类

DRAM的特点:主要由电容构成,需要定时刷新

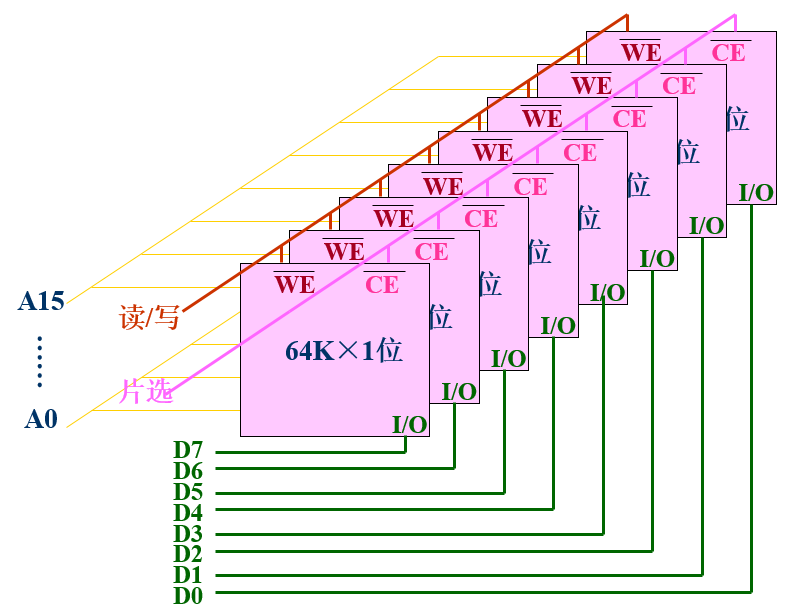

DRAM芯片举例:intel 2164A,容量为\(64k\times 1\)存储器扩展技术

存储器的存储容量等于:单元数(字节数)×每单元的位数(字长),因此就有三种扩容方式:字扩展、位扩展、字位扩展。位扩展

地址线、片选线和读写信号线各芯片共用,数据线单独引出。

eg:8片64K×1位的SRAM芯片构成容量为64KB的存储器

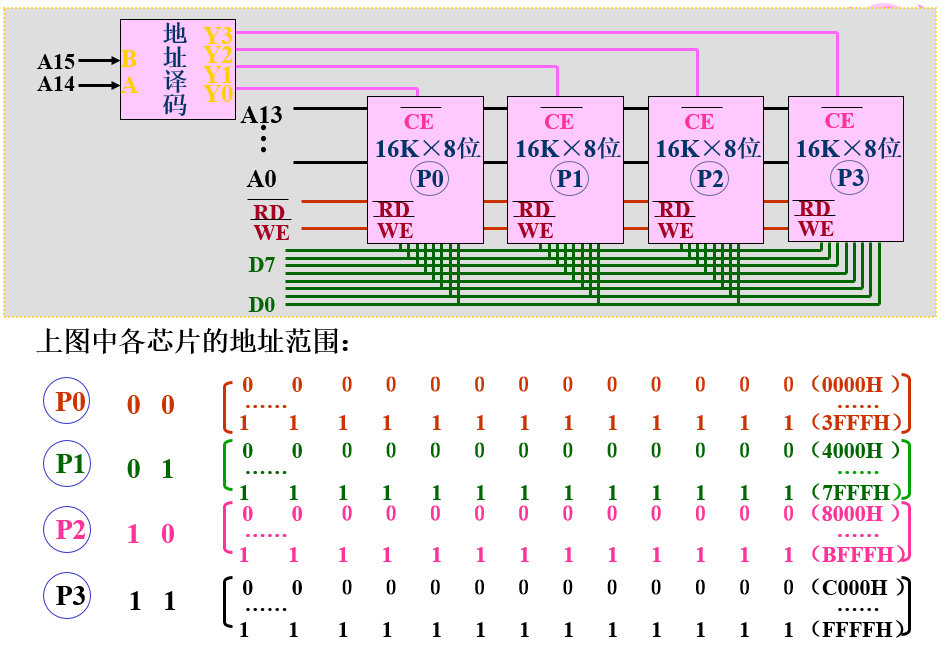

字扩展

地址线、读写信号线和数据线各芯片共用,片选线单独引出。

eg:4片16K×8位的SRAM芯片构成容量为64KB的存储器

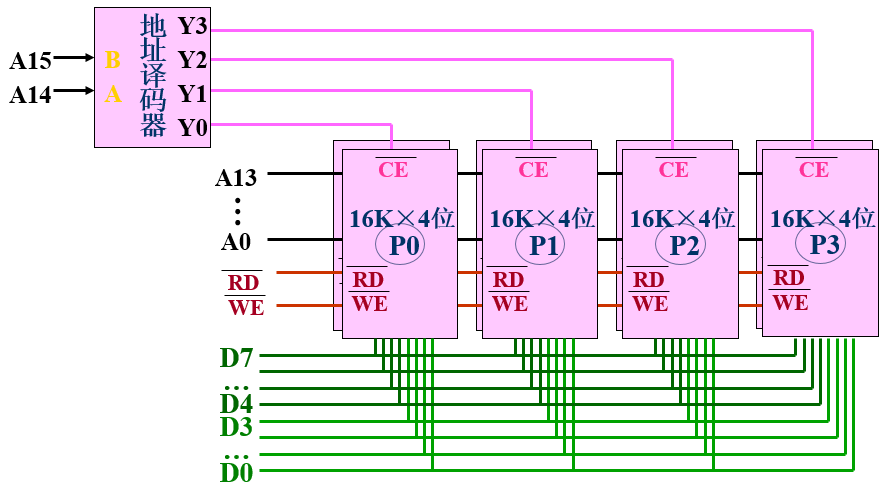

字位扩展

结合了上述两种方法的特点。

eg:用8片16K×4位的存储器芯片组成64K×8位的存储器

第九章 人机接口

键盘接口的分类

编码键盘:这种键盘内部能自动检测被按下的键,并提供与被按键对应的键码(如ASCII码),以并行或串行方式送给CPU。

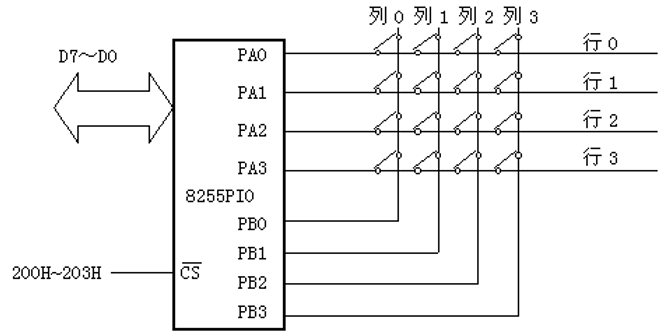

非编码键盘:这种键盘只提供键盘的行列矩阵,而按键的识别和键值的确定、输入等工作通过软件完成。这是目前可得到的最便宜的微机输入设备。软件实现非编码键盘识别的方法

扫描法:

依次查询键盘矩阵的每一行线,然后读取列数据确定按键是否在本行,具体方法如下:

首先使PA0=0,然后读取PB端口。

若PB=0FFH则表示行0没有按键按下,再使PA1=0再读取PB判断行2有无按键按下,依次扫描全部的行线。

当PB读取的数据不为0FFH,则表示该扫描行有按键按下,则再确定相应的按键序号。

时间复杂度:\(n^2\)

行列交换法:

使CPU通过A口向各行线上全部送低电平,然后从B口读入列线的值。

如果某按键按下,则必定会使某一列线值为0。然后,交换A口B口的输入输出方向,并将刚才读到的列线值从列线所接的并口输出。

再读取行线上的输入值,在闭合键所在的行线上的值必定为0。这样,当一个按键被按下时,必定可以读取一对唯一的行值和列值。

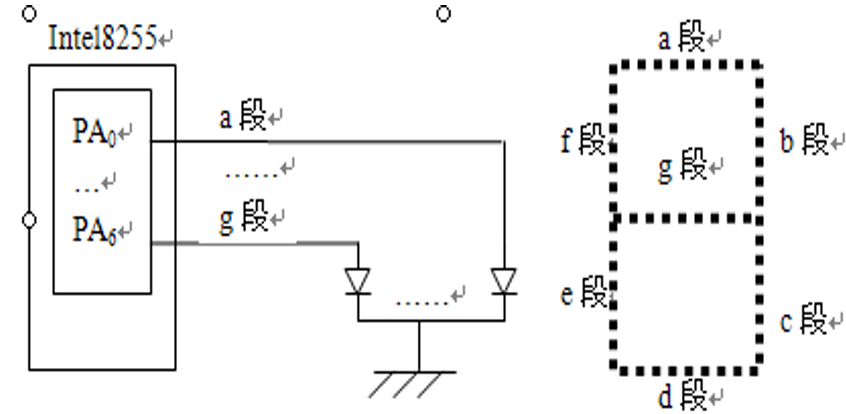

时间复杂度:\(2n\)七段数码管

七段数码管就是并行接口8255,7个段分别对应8255的一个引脚,通过设置引脚电平来控制亮灭,示意图如下:

Post Date: 2018-09-13

版权声明: 本文为原创文章,转载请注明出处